Apple

public://topics-images/apple_webp.png

SCB10X

public://topics-images/347823389_774095087711602_515970870797767330_n_webp.png

Windows 11

public://topics-images/hero-bloom-logo.jpg

Huawei

public://topics-images/huawei_standard_logo.svg_.png

Google Keep

public://topics-images/google_keep_2020_logo.svg_.png

Instagram

public://topics-images/instagram_logo_2022.svg_.png

Microsoft

public://topics-images/microsoft_logo.svg_.png

Basecamp

public://topics-images/bwpepdi0_400x400.jpg

FTC

public://topics-images/seal_of_the_united_states_federal_trade_commission.svg_.png

Pinterest

public://topics-images/pinterest.png

Palantir

public://topics-images/-nzsuc6w_400x400.png

AIS Business

public://topics-images/logo-business-2021-1.png

PostgreSQL

public://topics-images/images.png

JetBrains

public://topics-images/icx8y2ta_400x400.png

Krungthai

public://topics-images/aam1jxs6_400x400.jpg

Palworld

public://topics-images/mccyhcqf_400x400.jpg

Bill Gates

public://topics-images/bill_gates-september_2024.jpg

VMware

public://topics-images/1nj4i1gp_400x400.jpg

Take-Two Interactive

public://topics-images/0khle7nh_400x400.jpg

OpenAI

public://topics-images/ztsar0jw_400x400.jpg

Thailand

public://topics-images/flag_of_thailand.svg_.png

ServiceNow

public://topics-images/ytnrfphe_400x400.png

Klarna

public://topics-images/urcllpjp_400x400.png

Google Play

public://topics-images/play.png

Drupal

public://topics-images/drupal.png

Virtua Fighter

public://topics-images/virtua_figther_2024_logo.png

Paradox Interactive

public://topics-images/paradox_interactive_logo.svg_.png

Europa Universalis

public://topics-images/europa-icon.png

Nintendo Switch 2

public://topics-images/mainvisual.png

Cloudflare

public://topics-images/cloudflare_logo.svg_.png

Samsung

public://topics-images/samsung.png

Google

public://topics-images/google_2015_logo.svg_.png

Uber

public://topics-images/uber.png

Microsoft 365

public://topics-images/m365.png

USA

public://topics-images/flag_of_the_united_states.svg_.png

GM

public://topics-images/0pe0po-z_400x400.jpg

Perplexity

public://topics-images/perplex.jpg

Xperia

public://topics-images/xperia.png

iOS 18

public://topics-images/ios-18-num-96x96_2x.png

True

public://topics-images/true_logo.png

SoftBank

public://topics-images/softbank.jpg

Pac-Man

public://topics-images/pacman.png

Harry Potter

public://topics-images/harry.png

Marvel

public://topics-images/marvel.png

Skydance

public://topics-images/skydance.png

SEA

public://topics-images/sealogo.png

Find Hub

public://topics-images/find.png

Accessibility

public://topics-images/accessibility-128x128_2x.png

Material Design

public://topics-images/m3-favicon-apple-touch.png

Android 16

public://topics-images/android16.png

Android

public://topics-images/android_0.png

Firefox

public://topics-images/firefox_logo-2019.svg_.png

Google Messages

public://topics-images/messages.png

Notepad

public://topics-images/notepad.png

Singapore

public://topics-images/flag_of_singapore.svg_.png

Airbnb

public://topics-images/airbnb.png

PS5

public://topics-images/ps5.png

Krafton

public://topics-images/krafton.png

Doom

public://topics-images/doom-game-s_logo.svg_.png

AMD

public://topics-images/amd_logo.svg_.png

GTA

public://topics-images/gta_0.png

DoorDash

public://topics-images/doordash.png

YouTube

public://topics-images/yt.png

YouTube Music

public://topics-images/yt-music.png

Facebook

public://topics-images/fb.png

iQiyi

public://topics-images/iqiyi_0.png

Viu

public://topics-images/viu.png

Amazon Prime Video

public://topics-images/prime-vid.png

Spotify

public://topics-images/spotify.jpg

HBO Max

public://topics-images/max.png

Alexa

public://topics-images/alexa.png

Kindle App

public://topics-images/kindle.png

Shopee

public://topics-images/shopee.png

Waze

public://topics-images/waze.png

Bilibili

public://topics-images/bili.png

Google Maps

public://topics-images/maps.png

Apple Music

public://topics-images/apple-music.png

Claude

public://topics-images/claude.png

TikTok

public://topics-images/tiktok.png

Xbox

public://topics-images/xbox.png

Tesla

public://topics-images/tesla.png

Google Calendar

public://topics-images/gcal.png

Google Meet

public://topics-images/meet.png

NotebookLM

public://topics-images/notebooklm.png

Reddit

public://topics-images/reddit.png

Assassin’s Creed

public://topics-images/ac.png

Mark Zuckerberg

public://topics-images/zuck.jpg

Meta

public://topics-images/meta.png

Epic Games

public://topics-images/epic_games_logo.svg_.png

Unreal

public://topics-images/unreal_engine_logo-new_typeface-svg.png

Fortnite

public://topics-images/fortnite.png

DeepMind

public://topics-images/deepmind.png

Databricks

public://topics-images/databricks.png

Netflix

public://topics-images/netflix-logo.png

Microsoft Azure

public://topics-images/azure.png

Microsoft Copilot

public://topics-images/microsoft_copilot_icon.svg_.png

Bing

public://topics-images/bing.png

EA

public://topics-images/ea.png

Intel

public://topics-images/intel.png

Amazon

public://topics-images/amazon.png

AWS

public://topics-images/aws.png

Zoom

public://topics-images/zoom.png

Dropbox

public://topics-images/dropbox_0.png

Dell Technologies

public://topics-images/dell-tech.png

Nothing

public://topics-images/nothing.svg_.png

Microsoft Teams

public://topics-images/teams.png

Mojang

public://topics-images/mojang.png

Minecraft

public://topics-images/minecraft.png

Redis

public://topics-images/redis_logo.svg_.png

Ubisoft

public://topics-images/ubisoft_logo.svg_.png

Elden Ring

public://topics-images/elden.png

Brave

public://topics-images/brave.png

Opera

public://topics-images/opera.png

Vivaldi

public://topics-images/vivaldi.png

Microsoft Edge

public://topics-images/edge.png

Duolingo

public://topics-images/duolingo.png

LinkedIn

public://topics-images/linkedin.png

Canva

public://topics-images/canva.png

Realme

public://topics-images/realme.png

NASA

public://topics-images/nasa-logo.png

Booking.com

public://topics-images/booking.png

Agoda

public://topics-images/agoda.png

Bolt

public://topics-images/bolt.png

Temu

public://topics-images/temnu.png

LINE

public://topics-images/line.png

Facebook Messenger

public://topics-images/messenger.png

WhatsApp

public://topics-images/whatsapp.png

Telegram

public://topics-images/telegram.png

Signal

public://topics-images/signal.png

X.com

public://topics-images/x.png

Grok

public://topics-images/grok.png

xAI

public://topics-images/xai.png

CapCut

public://topics-images/capcut.png

Edits

public://topics-images/edit.png

Google One

public://topics-images/gone.png

Tinder

public://topics-images/tinger.png

Whoscall

public://topics-images/whoscall.png

OneDrive

public://topics-images/onedrive.png

Lightroom

public://topics-images/lr.png

Meitu

public://topics-images/meitu.png

Outlook

public://topics-images/outlook.png

Excel

public://topics-images/excel.png

PowerPoint

public://topics-images/ppt.png

Microsoft Word

public://topics-images/word.png

Phone Link

public://topics-images/phone-link.png

OneNote

public://topics-images/onenote.png

Windows App

public://topics-images/windows-app.png

Notion

public://topics-images/notion.png

Google Drive

public://topics-images/drive.png

YouTube Kids

public://topics-images/yt-kids.png

Gboard

public://topics-images/gboard.png

DeepSeek

public://topics-images/deepseek_logo.svg_.png

Prince of Persia

public://topics-images/prince-persia.png

Sony

public://topics-images/nq0nd2c0_400x400.jpg

Cisco

public://topics-images/jmyca1yn_400x400.jpg

Alibaba Cloud

public://topics-images/qm43orjx_400x400_cloud.png

Coinbase

public://topics-images/consumer_wordmark.png

CarPlay

public://topics-images/carplay.png

Rust

public://topics-images/rust-logo-blk.png

Red Hat

public://topics-images/redhat.png

Anthropic

public://topics-images/anthropic.png

Xcode

public://topics-images/xcode.png

Tim Cook

public://topics-images/tim-cook.jpg

Donald Trump

public://topics-images/trump.jpg

Microsoft Surface

public://topics-images/surface.jpg

Copilot+ PC

public://topics-images/copilotpc.png

Stellar Blade

public://topics-images/stellar-blade.jpg

Snapdragon

public://topics-images/snapdragon_chip.png

Qualcomm

public://topics-images/qualcomm-logo.svg_.png

CoreWeave

public://topics-images/coreweave.png

Ford

public://topics-images/ford.png

Xiaomi

public://topics-images/xiaomi.png

Google Cloud

public://topics-images/google_cloud_logo.svg_.png

PlayStation Network

public://topics-images/psn.png

PlayStation Plus

public://topics-images/ps-plus.png

Windsurf

public://topics-images/windsurf.png

Square Enix

public://topics-images/square-enix.png

MIT

public://topics-images/x7hyjl3t_400x400.jpg

Zoox

public://topics-images/zoox.jpg

Evernote

public://topics-images/1neatidg_400x400.jpg

Magic the Gathering

public://topics-images/magic.png

Call of Duty

public://topics-images/cod.png

NVIDIA

public://topics-images/nvidia_logo.svg_.png

Satya Nadella

public://topics-images/nadella.png

Nintendo

public://topics-images/nintendo.png

Japan

public://topics-images/japan_flag.png

China

public://topics-images/china-flag-sq.png

Sam Altman

public://topics-images/sam-altman.png

SNK

public://topics-images/snk_logo.svg_.png

EPYC

public://topics-images/epyc.png

Juniper

public://topics-images/juniper.png

CMA

public://topics-images/cma.png

App Store

public://topics-images/app-store.png

DoJ

public://topics-images/doj.png

Siri

public://topics-images/siri.png

Apple Intelligence

public://topics-images/apple-intelligence.png

Acer

public://topics-images/acer.png

GeForce

public://topics-images/geforce.png

Omen

public://topics-images/omen.png

Alienware

public://topics-images/alienware.png

Dell

public://topics-images/dell.png

Bungie

public://topics-images/bungie.png

Marathon

public://topics-images/marathon.png

Intel Arc

public://topics-images/badge-arc-graphics.png

GitHub

public://topics-images/8zfrryja_400x400.png

GitHub Copilot

public://topics-images/copilot.png

Foxconn

public://topics-images/foxconn_0.png

Visual Studio

public://topics-images/vs.png

Visual Studio Code

public://topics-images/vscode.png

WSL

public://topics-images/wsl.png

Linux

public://topics-images/linux.png

Tencent

public://topics-images/tencent_logo_2017.svg_.png

Entra

public://topics-images/microsoft_entra_id_color_icon.svg_.png

RHEL

public://topics-images/rhel-icon.png

MSI

public://topics-images/msi-logo-for_digital_use_b.png

MCP

public://topics-images/mcp.png

Docker

public://topics-images/docker.png

RISC-V

public://topics-images/risc-v-logo.svg_.png

Fedora

public://topics-images/fedora.png

ASUS

public://topics-images/asus.png

ROG

public://topics-images/rog-logo_red.png

Naughty Dog

public://topics-images/naughty-dog.png

AIS

public://topics-images/357073423_657473419752809_8491928084596189631_n.png

National Telecom

public://topics-images/nt.jpg

Elon Musk

public://topics-images/elon_musk_2015_0.jpg

OpenShift

public://topics-images/openshift-logotype.svg-0.png

Shift Up

public://topics-images/shiftup.png

Bethesda

public://topics-images/bethesda.png

The Elder Scrolls

public://topics-images/tes.png

CATL

public://topics-images/img_7841.png

Radeon

public://topics-images/radeon.png

Borderlands

public://topics-images/borderlands4.png

Android XR

public://topics-images/android-xr.png

Ninja Theory

public://topics-images/ninja.jpg

Jonathan Ive

public://topics-images/ive.jpg

Bitcoin

public://topics-images/bitcoin.svg_.png

Baidu

public://topics-images/baidu.jpg

Wear OS

public://topics-images/wearos.png

Activision

public://topics-images/activision.svg_.png

Netmarble

public://topics-images/netmarble.png

NetEase

public://topics-images/netease.png

Fujifilm

public://topics-images/l_9ycfw2_400x400.png

Google Vids

public://topics-images/vids.png

Google Docs

public://topics-images/docs.png

Google Sheets

public://topics-images/sheets.png

Google Chat

public://topics-images/gchat.png

Google Slides

public://topics-images/slides.png

Google Photos

public://topics-images/photos_0.png

Snapchat

public://topics-images/snapchat.png

Google TV

public://topics-images/gtv.png

Android Auto

public://topics-images/aauto.png

Gmail

public://topics-images/gmail.png

Google Forms

public://topics-images/forms.png

Google Workspace

public://topics-images/workspace_0.png

Android Studio

public://topics-images/android_studio_logo_2024.svg_.png

Pocket

public://topics-images/spnhfky8_400x400.png

Mozilla

public://topics-images/mozilla.jpg

Thunderbird

public://topics-images/thunderbird.png

Bluesky

public://topics-images/bluesky.jpg

Warhammer

public://topics-images/warhammer-bw.png

Relic Entertainment

public://topics-images/relic_entertainment_logo.svg_.png

Age of Empires

public://topics-images/age_of_empires_franchise_logo.png

Azul

public://topics-images/azul.png

Meta Quest

public://topics-images/meta-quest.png

Informatica

public://topics-images/qzlzwpsp_400x400.jpg

Salesforce

public://topics-images/salesforce.com_logo.svg_.png

Steam

public://topics-images/steam.png

Valve

public://topics-images/valve_logo.svg_.png

SteamOS

public://topics-images/steamos_wordmark.svg_.png

Steam Deck

public://topics-images/steam-deck.png

Arch Linux

public://topics-images/archlinux-logo-standard-version.svg_.png

Half-Life

public://topics-images/orange_lambda.svg_.png

Counter-Strike

public://topics-images/counter-strike.png

OnlyFans

public://topics-images/onlyfans_logo_icon_blue.png

Strava

public://topics-images/strava.png

Mortal Kombat

public://topics-images/mortal-kombat.png

Canon

public://topics-images/canon.png

Snipping Tool

public://topics-images/snipping.png

Microsoft Paint

public://topics-images/paint.png

Microsoft Photos

public://topics-images/photos.png

File Explorer

public://topics-images/file_explorer.png

Git

public://topics-images/git-logo.svg_.png

Star Wars

public://topics-images/star-wars.png

Activision Blizzard

public://topics-images/actvision-blizz.png

Microsoft Store

public://topics-images/microsoft-store.png

France

public://topics-images/france.png

Ricoh

public://topics-images/ricoh_logo_2005.svg_.png

Xeon

public://topics-images/xeon.png

.NET

public://topics-images/dotnet.png

SQL Server

public://topics-images/microsoft_sql_server_2025_icon.svg_.png

Power BI

public://topics-images/power-bi.png

Microsoft Fabric

public://topics-images/fabric.png

MSN

public://topics-images/msn.png

SharePoint

public://topics-images/sharepoint.png

Ubuntu

public://topics-images/ubuntu-logo-2022.svg_.png

Debian

public://topics-images/debian-openlogo.svg_.png

LLM

public://topics-images/7410e129-824e-479c-93c7-558e87130b8f.png

Meituan

public://topics-images/meituan.png

Logitech

public://topics-images/logitech_logo.svg_.png

Llama

public://topics-images/llama.png

Oracle

public://topics-images/oracle_logo.svg_.png

Circle

public://topics-images/circle.png

T-Mobile

public://topics-images/tmobile.jpg

Starlink

public://topics-images/starlink.jpg

SpaceX

public://topics-images/hbri04tm_400x400.jpg

Apple Arcade

public://topics-images/en-us-large-1x.png

TypeScript

public://topics-images/typescript.svg_.png

AlmaLinux

public://topics-images/almalinux.png

Subnautica

public://topics-images/subnautica.png

Clair Obscur

public://topics-images/clair-33.png

Dragon Quest

public://topics-images/dragon_quest_logo.png

Twitter

public://topics-images/twitter300.png

One UI

public://topics-images/one-ui.png

Fire TV

public://topics-images/amazon_fire_tv_2024.svg_.png

Stellantis

public://topics-images/stellantis.png

Taobao

public://topics-images/taobao.png

WeChat

public://topics-images/wechat.png

Alipay

public://topics-images/alipay.png

DingTalk

public://topics-images/dingtalk.png

Alibaba

public://topics-images/alibaba-group-logo.svg_.png

Pokemon

public://topics-images/international_pokemon_logo.svg_.png

NBTC

public://topics-images/nbtc.png

CD Projekt

public://topics-images/cd_projekt_logo.svg_.png

Cyberpunk 2077

public://topics-images/cyberpunk.png

The Witcher

public://topics-images/witcher.png

Boeing

public://topics-images/boeing.png

Discord

public://topics-images/discord.png

Grammarly

public://topics-images/grammarly.png

Google Lens

public://topics-images/lens.png

WordPress

public://topics-images/wordpress.png

Automattic

public://topics-images/automattic.png

Zotac

public://topics-images/zotac.png

Black Forest Labs

public://topics-images/flux.png

Sega

public://topics-images/sega.png

Twitch

public://topics-images/twitch.png

Person

public://topics-images/gemini_generated_image_ddj47iddj47iddj4.png

IntelliJ

public://topics-images/intellij.png

CrowdStrike

public://topics-images/cs_logo.png

Bandai Namco

public://topics-images/bandainamco.png

Oppo

public://topics-images/oppo.png

Dontnod

public://topics-images/don-t_nod.png

Hugging Face

public://topics-images/huggingface.png

Bixby

public://topics-images/logo_bixby_new.svg_.png

Gemma

public://topics-images/gemma.png

Flash Express

public://topics-images/flash.png

Lyft

public://topics-images/lyft.png

James Bond

public://topics-images/007.png

Snowflake

public://topics-images/snowflake.png

IO Interactive

public://topics-images/ioi.png

The Sims

public://topics-images/the_sims.png

Character.AI

public://topics-images/character_ai.png

IBM

public://topics-images/xy93qvy4_400x400.png

USB

public://topics-images/usb-logo.png

Zynga

public://topics-images/zynga.svg_.png

Broadcom

public://topics-images/broadcom.png

Photoshop

public://topics-images/ps.png

Adobe

public://topics-images/adobe.png

Premiere Pro

public://topics-images/premier.png

Database

public://topics-images/gemini_generated_image_nlgayenlgayenlga.png

GeForce Now

public://topics-images/gf-now.png

Go

public://topics-images/o6aczwfv_400x400.png

ChatGPT

public://topics-images/chatgpt.png

Final Fantasy

public://topics-images/ff.png

Swift

public://topics-images/swift_logo.svg_.png

Cursor

public://topics-images/cursor.png

AirPods Max

public://topics-images/airpodsmax.png

Koei Tecmo

public://topics-images/koei_tecmo.png

Team Ninja

public://topics-images/team-ninja.png

Disney+

public://topics-images/disney-plus.png

Capcom

public://topics-images/capcom.png

Pornhub

public://topics-images/pornhub-logo.svg_.png

Proton

public://topics-images/proton.png

PlayStation

public://topics-images/playstation.png

GOG

public://topics-images/gog-logo.png

Mistral

public://topics-images/mistral.png

No Man's Sky

public://topics-images/nomansky.png

Hello Games

public://topics-images/hello-games-logo.png

SCB

public://topics-images/scb.png

Kasikorn Bank

public://topics-images/kbank.png

Grasshopper Manufacture

public://topics-images/grasshopper-100.png

Metal Gear

public://topics-images/metal_gear_franchise_logo.svg_.png

Google Wallet

public://topics-images/g-wallet.png

PayPal

public://topics-images/paypal.png

Mark Cuban

public://topics-images/cuban.jpg

Giant Squid

public://topics-images/giant-squid.png

Black Myth: Wukong

public://topics-images/blackmyth.jpg

Deathloop

public://topics-images/deathloop_logo.webp_.png

Resident Evil

public://topics-images/residentevil.png

Street Fighter

public://topics-images/street_fighter_logo.png

Ryu Ga Gotoku

public://topics-images/ryugagotokustudio.png

Like a Dragon

public://topics-images/lad-logo.png

Sonic the Hedgehog

public://topics-images/sonic.png

Blender

public://topics-images/logo_blender.svg_.png

Volvo

public://topics-images/volvo-iron-mark-black.svg_.png

Atomic Heart

public://topics-images/atomic.png

Hitman

public://topics-images/hitman.png

Mac

public://topics-images/apple-finder.png

Arc Raiders

public://topics-images/arc-raiders.jpg

Krungsri Bank

public://topics-images/krungsri.png

Owlcat Games

public://topics-images/owlcat.png

Scale

public://topics-images/scale_ai.png

The Outer Worlds

public://topics-images/1600px-outerworlds-logo.png

Obsidian Entertainment

public://topics-images/obsidian_entertainment.svg_.png

Avowed

public://topics-images/avowed.png

Grounded

public://topics-images/grounded.png

Atlus

public://topics-images/atlus_logo_thin_stroke_277x108.png

High on Life

public://topics-images/high-logo.png

Ryzen

public://topics-images/ryzen.png

Flight Simulator

public://topics-images/microsoft_flight_simulator.png

Indiana Jones

public://topics-images/indiana_jones_logo.svg_.png

Dawnwalker

public://topics-images/the-blood-of-dawnwalker-logo-light.png

Rebel Wolves

public://topics-images/rebel-wolves-logo-black.png

inXile

public://topics-images/inxile_entertainment_logo.png

Double Fine Productions

public://topics-images/double-fine.png

Game Freak

public://topics-images/game_freak_logo.svg_.png

iOS 26

public://topics-images/ios26.png

Tahoe

public://topics-images/macos26.png

iPadOS 26

public://topics-images/ipados26.png

Zelda

public://topics-images/zelda_logo.svg_.png

watchOS 26

public://topics-images/watchos26.png

Apple Vision Pro

public://topics-images/applevisionpro.png

Amiibo

public://topics-images/amiibo.png

Thunder Lotus

public://topics-images/thunder-lotus.png

Games

public://topics-images/role-playing_video_game_icon.svg_.png

Waymo

public://topics-images/waymo.png

Grab

public://topics-images/grab_0.png

Fallout

public://topics-images/fallout_logo.svg_.png

Warner Bros. Discovery

public://topics-images/wbd.png

Splatoon

public://topics-images/splatoon.png

Kingston

public://topics-images/kingston.png

Roblox

public://topics-images/roblox_thumb.png

Google Pixel

public://topics-images/pixel_wordmark.svg_.png

Jensen Huang

public://topics-images/jensen-headshot-1906-600x338.png

Midjourney

public://topics-images/61396273.png

NBCUniversal

public://topics-images/umh_w5l-400x400.png

Disney

public://topics-images/disney.png

Snap

public://topics-images/snap_inc.png

Wikipedia

public://topics-images/wikipedia-logo-v2.svg_.png

Kaggle

public://topics-images/kaggle_logo.svg_.png

Wikimedia Foundation

public://topics-images/wikimedia_foundation.png

IonQ

public://topics-images/ionq.png

Apple TV+

public://topics-images/apple_tv_plus.png

Slack

public://topics-images/slack.png

Webex

public://topics-images/webex.png

Wayland

public://topics-images/wayland.png

GNOME

public://topics-images/gnomelogo.svg_.png

X.Org

public://topics-images/xorg.png

PCI-SIG

public://topics-images/pci-sig_logo.png

PCI

public://topics-images/pci_express.svg_.png

Instinct

public://topics-images/instinct.png

MariaDB

public://topics-images/img_9067.png

Mattel

public://topics-images/mattel-2019-svg.png

Silent Hill

public://topics-images/silent_hill_2022_logo.png

Bloober Team

public://topics-images/blooberlogo260b.png

India

public://topics-images/flag_of_india.png

Nexon

public://topics-images/nexon.svg_.png

Helldivers

public://topics-images/helldivers_print_logo.png

Mac Mini

public://topics-images/mac-mini-202410-gallery.png

Dyson

public://topics-images/dyson.png

Mario Kart

public://topics-images/mario-kart-100.png

Germany

public://topics-images/flag_of_germany.svg_.png

Gears of War

public://topics-images/gears-of-war-logo-2006.png

Warren Buffett

public://topics-images/buffett.png

Craig Federighi

public://topics-images/craige1.png

Boston Dynamics

public://topics-images/boston.png

aespa

public://topics-images/aespa.png

NewJeans

public://topics-images/newjeans.png

iPhone 16

public://topics-images/iphone16_.png

iPhone 16 Pro

public://topics-images/iphone16_pro.png

Indonesia

public://topics-images/indo_flag.png

Devil May Cry

public://topics-images/dmc5.png

Etsy

public://topics-images/etsy.png

Ghost of Yōtei

public://topics-images/ghost.png

BT

public://topics-images/bt_logo_2019.svg_.png

Kubernetes

public://topics-images/kubernetes_logo_without_workmark.svg_.png

Pixelfed

public://topics-images/pixelfed.png

Mastodon

public://topics-images/mastodon.png

Iran

public://topics-images/iran.png

Israel

public://topics-images/flag_of_israel.png

Warner Bros.

public://topics-images/warner_bros.png

Qwen

public://topics-images/qwenpng.png

Donkey Kong

public://topics-images/dk.png

Mario

public://topics-images/mario.png

Honda

public://topics-images/kln5su0v_400x400.jpg

Wix

public://topics-images/wix.png

Google Tensor

public://topics-images/ggtensor.png

Bank of Thailand

public://topics-images/bankofthailand.png

Beat Saber

public://topics-images/beat.png

PlayStation VR

public://topics-images/psvr2.png

Texas Instrument

public://topics-images/ti.png

NFC

public://topics-images/daak0pur_400x400.jpg

LG

public://topics-images/lg.png

EA Sports FC

public://topics-images/ea-fc.png

Volkswagen

public://topics-images/volkswagen_logo_2019.svg_.png

Disco Elysium

public://topics-images/disco.png

Neowiz

public://topics-images/neowiz_holdings_logo.png

Lies of P

public://topics-images/lies-p.png

Thinking Machines Lab

public://topics-images/u6tsxu60_400x400_0.png

Mira Murati

public://topics-images/-pnysxgr_400x400.png

Vimeo

public://topics-images/vimeo.png

Japan Airlines

public://topics-images/jal.png

HarmonyOS

public://topics-images/harmonyos_logo.png

Sequoia

public://topics-images/sequoia.png

iPadOS 18

public://topics-images/ipados-18-num-96x96_2x.png

Sakana AI

public://topics-images/dtnrodgp_400x400.png

Runway

public://topics-images/lpx3j0s7_400x400.png

Exynos

public://topics-images/exynos.png

MediaTek

public://topics-images/mediatek_logo.svg_.png

Arm

public://topics-images/arm.png

Facebook Groups

public://topics-images/groupslogo2.png

Death Stranding

public://topics-images/death_stranding_logo.png

Bumble

public://topics-images/bumble.png

Rematch

public://topics-images/logorematch_transcreen.png

GWM

public://topics-images/2025-gwm-logo-rgb-digital_2.png

Barclays

public://topics-images/barclays_logo.svg_.png

Asana

public://topics-images/asana.png

Dying Light

public://topics-images/dying-light-200.png

Creative Commons

public://topics-images/apple-touch-icon.png

EU

public://topics-images/flag-for-european-union_1f1ea-1f1fa.png

Cambodia

public://topics-images/flag_of_cambodia.svg_.png

HDMI

public://topics-images/high_definition_multimedia_interface_logo.svg_.png

Denmark

public://topics-images/denmark-flag.png

Riot Games

public://topics-images/riot_games_2022.svg_.png

League of Legends

public://topics-images/lol.png

Valorant

public://topics-images/valorant.png

Pioneer

public://topics-images/459525305_7951848951587833_4839605414563613731_n.png

Google Earth

public://topics-images/gearth.png

Google TV Streamer

public://topics-images/gtv_0.png

Chromecast

public://topics-images/chromecast.png

Fairphone

public://topics-images/fairphone.png

Honor

public://topics-images/honor_logo-2020-svg.png

Counterpoint Research

public://topics-images/counterpoint.png

BBC

public://topics-images/bbc.png

TrueMove H

public://topics-images/334187583_158099563725447_7727972013376860320_n.png

AliExpress

public://topics-images/aliexpress.png

Norway

public://topics-images/flag_of_norway.svg_.png

Research

public://topics-images/research-icon.png

Science

public://topics-images/science.png

Figma

public://topics-images/wpgpzf_m_400x400.png

Gemini

public://topics-images/gemini-colors.png

Social Security

public://topics-images/social-security.png

Hikvision

public://topics-images/cdyc5hhc_400x400.png

Autodesk

public://topics-images/autodesk_logo_2021.svg_.png

Rare

public://topics-images/rare_logo_2015.svg_.png

Sea of Thieves

public://topics-images/sea-of-thieves.png

Skype

public://topics-images/skype.png

Safe Superintelligence

public://topics-images/ssi.png

PowerShell

public://topics-images/powershell_256.png

Apple Store

public://topics-images/apple_store.png

Battlefield

public://topics-images/battlefieldlogo.svg_.png

Robinhood

public://topics-images/1ftlyz2c_400x400.png

Malaysia

public://topics-images/malaysia-flag.png

Forza

public://topics-images/forza_logo_2020.svg_.png

John Romero

public://topics-images/romero.jpg

TSMC

public://topics-images/tsmc_1.png

Vietnam

public://topics-images/flag_of_vietnam.svg_.png

React

public://topics-images/react.png

KPLUS

public://topics-images/kplus.png

Jack Dorsey

public://topics-images/jack.jpg

Replit

public://topics-images/replit.png

GlobalFoundries

public://topics-images/gf.png

MIPS

public://topics-images/mips.png

Linda Yaccarino

public://topics-images/c5dthmbt.png

GameStop

public://topics-images/ouc1sr_p_400x400.png

Belkin

public://topics-images/belkin_logo_2024.svg_.png

Home Assistant

public://topics-images/home-assistant.png

Next.js

public://topics-images/if82cpbs_400x400.jpg

Hertz

public://topics-images/hertz_car_rental_logo.svg_.png

Jio

public://topics-images/jio.png

Lucid Motors

public://topics-images/lucidmotor.png

Guinness World Record

public://topics-images/gwr.png

EFF

public://topics-images/eff.png

TIOBE

public://topics-images/tiobe.png

MLX

public://topics-images/102832242.png

DoD

public://topics-images/dod.png

IDC

public://topics-images/idc.png

OpenGL

public://topics-images/opengl_logo.svg_.png

Vulkan

public://topics-images/vulkan_logo.svg_.png

NIST

public://topics-images/hp8oa5cb_400x400.png

ASML

public://topics-images/img_1736.jpeg

Curl

public://topics-images/curl_icon.png

Google Assistant

public://topics-images/assistant.png

ChromeOS

public://topics-images/chromeos_logo.svg_.png

Adobe Firefly

public://topics-images/firefly.png

SonicWall

public://topics-images/sonicwall.png

Astronomer

public://topics-images/astro.jpg

Corning

public://topics-images/corning.png

Emoji

public://topics-images/emoji.png

CUDA

public://topics-images/nvidia_cuda.png

Ready or Not

public://topics-images/readyornot-logo.png

Google Tasks

public://topics-images/gtasks.png

Qi

public://topics-images/qi.png

Lego

public://topics-images/lego_logo.svg_.png

Game Boy

public://topics-images/nintendo_game_boy_logo.svg_.png

SK Hynix

public://topics-images/img_2498.png

Sonos

public://topics-images/sonos_logo.png

Eidos

public://topics-images/eidos_montreal.png

Tomb Raider

public://topics-images/tomb_raider_logo_2022.png

Guardians of the Galaxy

public://topics-images/guardians_of_the_galaxy-logo.png

Kindle

public://topics-images/kindle-smile-logo.png

Amazon Prime

public://topics-images/prime.png

Amazon Luna

public://topics-images/amazon-luna-logo.png

Moon Studios

public://topics-images/moon.png

Ghost Recon

public://topics-images/ghost_recon_logo.png

Wolfenstein

public://topics-images/wolfenstein_logo.svg_.png

Pony.ai

public://topics-images/img_2799.png

Premier League

public://topics-images/pl-logo-light.png

Horizon

public://topics-images/horizon_game_series_logo.png

Exchange

public://topics-images/exchange_1500x1500.png

Mercedes-Benz

public://topics-images/mercedes_benz-logo.png

Django

public://topics-images/django_logo.svg_.png

Apple Card

public://topics-images/apple-card.png

JPMorgan

public://topics-images/logo-jpm-brown.png

Bitchat

public://topics-images/img_6038.png

Palo Alto Networks

public://topics-images/img_6100.png

KBTG

public://topics-images/c8qypege_400x400.jpg

Linux Foundation

public://topics-images/lf_sustainability_banner.png

Octopath Traveler

public://topics-images/project_octopath_traveler_logo.png

Monster Hunter

public://topics-images/monster_hunter_logo.png

Hideo Kojima

public://topics-images/kojima.jpg

Nintendo Switch

public://topics-images/switch1.png

Cerebras

public://topics-images/celebras.png

2K Games

public://topics-images/2k_2021_logo.svg_.png

BioShock

public://topics-images/bioshock-logo.svg_.png

Australia

public://topics-images/flag_of_australia.png

Groq

public://topics-images/groq.png

Ukraine

public://topics-images/flag_of_ukraine.svg_.png

Delta Air Lines

public://topics-images/o1z2hvzv_400x400.jpg

SAP

public://topics-images/img_8162.png

Audible

public://topics-images/lj9g-ikl_400x400.png

Vine

public://topics-images/vine_logo.svg_.png

THQ Nordic

public://topics-images/thq_nordic_logo_2016.svg_.png

Darksiders

public://topics-images/darksiders_logo.png

Embracer Group

public://topics-images/embracer_group_logo.svg_.png

Kingdom Come

public://topics-images/kcd2-banner-2.png

Gearbox

public://topics-images/gearbox_software_logo.svg_.png

Rockstar

public://topics-images/rockstar.png

Amazon Games

public://topics-images/amazon_games_logo.svg_.png

New World

public://topics-images/new-world.png

Crystal Dynamics

public://topics-images/cd.png

Metro Games

public://topics-images/metro.png

Supermicro

public://topics-images/img_8331.png

Genshin Impact

public://topics-images/genshin_impact_logo.svg_.png

Tan Lip-Bu

public://topics-images/img_8326.jpeg

Hulu

public://topics-images/hulu.png

iFixit

public://topics-images/ifixit_logo.svg_.png

Nightdive Studios

public://topics-images/nightdive_studios.svg_.png

id Software

public://topics-images/id_software.svg_.png

Quake

public://topics-images/quake.png

Astro

public://topics-images/astro.png

Zend

public://topics-images/logo-zend-reg.png

PHP

public://topics-images/php-logo.svg_.png

Framework Laptop

public://topics-images/framework.png

WebKit

public://topics-images/webkit_logo-2023-svg.png

Safari

public://topics-images/safari.png

Diablo

public://topics-images/diablo.png

Warcraft

public://topics-images/warcraft_logo.png

Blizzard

public://topics-images/blizzard_entertainment_logo_2015.svg_.png

Overwatch

public://topics-images/overwatch_circle_logo.svg_.png

World of Warcraft

public://topics-images/logo-wow.png

Hearthstone

public://topics-images/hearthstone.png

HandBrake

public://topics-images/handbrake.png

AOL

public://topics-images/hkam9td-400x400.png

Yahoo!

public://topics-images/yahoo.png

PayPay

public://topics-images/paypay.png

WinRAR

public://topics-images/winrar.png

ESET

public://topics-images/eset.png

Internet Archive

public://topics-images/bygruzmj_400x400.png

OpenSSH

public://topics-images/2387206.png

Vodafone

public://topics-images/vodafone.png

Verizon

public://topics-images/verizon.png

Microsoft Defender

public://topics-images/defender.png

Cryptocurrency

public://topics-images/bitcoin.svg__0.png

LINE Webtoon

public://topics-images/naver_line_webtoon_logo.png

Google News

public://topics-images/google-news.png

Pebble

public://topics-images/pebble.png

FFmpeg

public://topics-images/ffmpeg_logo_new.svg_.png

VLC

public://topics-images/vlc_icon.svg_.png

AV1

public://topics-images/av1_logo_2018.svg_.png

Football Manager

public://topics-images/fm.png

United Kingdom

public://topics-images/flag_of_the_united_kingdom.png

Python

public://topics-images/python-logo-notext.svg_.png

DuckDuckGo

public://topics-images/duck.png

nginx

public://topics-images/nginx.png

Google Translate

public://topics-images/google-translate.png

Parag Agrawal

public://topics-images/parag.jpg

VirtualBox

public://topics-images/virtualbox_2024_logo.svg_.png

Google Flights

public://topics-images/travel_flights_96dp_maskable.png

Posit

public://topics-images/posit-logo-2024.png

Apple Health

public://topics-images/apple-health.png

BMW

public://topics-images/bmw.svg_.png

Node.js

public://topics-images/node.js_logo.svg__0.png

Workday

public://topics-images/qa8vjtrt_400x400.png

MSNBC

public://topics-images/msnbc_2023.svg_.png

PuTTY

public://topics-images/screenshot-2025-08-20-at-00.23.08.png

Batman

public://topics-images/batman.png

LibreOffice

public://topics-images/libreoffice.png

Google Pixel 10

public://topics-images/pixel10_.png

Pixel Watch

public://topics-images/watch.png

Google Pixel Buds

public://topics-images/buds-2a.png

Ghost of Tsushima

public://topics-images/gotlogo.png

Fitbit

public://topics-images/fitbit.png

Hollow Knight

public://topics-images/silksong-cover.png

Tropico

public://topics-images/tropico_logo.png

DirectX

public://topics-images/directx.png

ROG Ally

public://topics-images/rog-ally.png

FBI

public://topics-images/seal_of_the_federal_bureau_of_investigation.svg_.png

ZA/UM

public://topics-images/zaum.png

Saudi Arabia

public://topics-images/flag_of_saudi_arabia.png

Niantic Labs

public://topics-images/niantic.png

Pokemon Go

public://topics-images/pokemon-go.png

Scopely

public://topics-images/scopely.png

Monopoly

public://topics-images/monopoly.png

Transformers

public://topics-images/transformers_2014_logo.png

Hashbro

public://topics-images/hasbro_logo.svg_.png

Sony Pictures

public://topics-images/sony_pictures_inc-logo.svg_.png

Angry Birds

public://topics-images/angry_birds_promo_art.png

Atom Text Editor

public://topics-images/atom.png

Electron

public://topics-images/electron.png

Zed

public://topics-images/zed.png

Finland

public://topics-images/flag_of_finland.svg_.png

South Korea

public://topics-images/flag_of_south_korea.png

Xbox Game Pass

public://topics-images/xbox_game_pass.png

HP

public://topics-images/hp_new.png

Taylor Swift

public://topics-images/img_0838.png

Atari

public://topics-images/atari_official_2012_logo.svg_.png

BYD

public://topics-images/byd_auto_2022_logo.svg_.png

Stardew Valley

public://topics-images/stardew.png

Escape From Tarkov

public://topics-images/tarkov.png

McDonalds

public://topics-images/mcdonalds.png

Taco Bell

public://topics-images/taco-bell-icon.png

Fastly

public://topics-images/fastly_logo.svg_.png

Bangkok Bank

public://topics-images/bangkok-bank.png

Dolby

public://topics-images/dolby.png

Hisense

public://topics-images/hisense.png

Sharp

public://topics-images/sharp.png

Toshiba

public://topics-images/toshiba.png

Anker

public://topics-images/ankerpng.png

EVO

public://topics-images/evo_championship_series_logo.png

MrBeast

public://topics-images/img_1683.jpeg

Garmin

public://topics-images/garmin.png

HPE

public://topics-images/img_1744.png

Atlassian

public://topics-images/atlassian.png

The Browser Company

public://topics-images/browser-company.png

ThinkPad

public://topics-images/thinkpad_logo.svg_.png

Lenovo

public://topics-images/lenovo-2015-svg_0.png

European Commission

public://topics-images/eu-com.png

Firaxis Games

public://topics-images/firaxis.png

AppLovin

public://topics-images/9qvw0l4x_400x400.png

OnePlus

public://topics-images/oneplus.png

Beats

public://topics-images/beats.png

VK

public://topics-images/vk.png

Russia

public://topics-images/flag_of_russia.png

Wargaming

public://topics-images/wg.png

Nebius

public://topics-images/tcowockq_400x400.png

AirPods

public://topics-images/airpodspro3.png

Apple Watch

public://topics-images/watch11.png

Apple Watch Ultra

public://topics-images/watchultra3.png

iPhone 17 Pro

public://topics-images/ip17_pro.png

iPhone Air

public://topics-images/iphoneair.png

iPhone 17

public://topics-images/iphone17.png

Apple Watch SE

public://topics-images/applewatchse.png

Unicode

public://topics-images/13873561.jpeg

Bending Spoons

public://topics-images/bending.png

Larry Ellison

public://topics-images/larryel.png

Stability AI

public://topics-images/stability_ai-wordmark.png

NPM

public://topics-images/npm.png

F5 Networks

public://topics-images/f5_400.png

HMD

public://topics-images/hmd_global_logo_2024.png

Fire Emblem

public://topics-images/fire_emblem_logo.svg_.png

FDA

public://topics-images/untvhciq_400x400.jpg

Hades

public://topics-images/hades-2-logo.png

Metroid

public://topics-images/metroid_logo_2017.svg_.png

Nova Launcher

public://topics-images/nova.png

Alphabet

public://topics-images/alphabet.png

Webtoon

public://topics-images/webtoon1.png

Ray-Ban

public://topics-images/ray-ban_logo.svg_.png

Java

public://topics-images/java_programming_language_logo.svg_.png

StubHub

public://topics-images/stubhub.png

Oakley

public://topics-images/oakley_logo.svg_.png

Horizon Worlds

public://topics-images/meta-horizon.png

Netskope

public://topics-images/netskope.png

WebAssembly

public://topics-images/webassembly_logo.svg_.png

Roku

public://topics-images/roku.png

AYANEO

public://topics-images/ayaneo.png

AKB48

public://topics-images/akb48.png

Northrop Grumman

public://topics-images/northrop_grumman.png

True ID

public://topics-images/true-id.png

Google Play Games

public://topics-images/gg-play-games.png

Insomniac

public://topics-images/insomniac_games.png

Deus Ex

public://topics-images/deus_ex_universe_logo.png

Housemarque

public://topics-images/housemarque.svg_.png

Google Search

public://topics-images/google-search-app.png

Raspberry Pi

public://topics-images/x9zmzhi9_400x400.jpg

eBay

public://topics-images/img_4817.jpeg

Klook

public://topics-images/klook.png

Google Home

public://topics-images/new-google-home.png

Jules

public://topics-images/jules.png

Supabase

public://topics-images/supabase.png

Firebase

public://topics-images/firebase.png

Peter Molyneux

public://topics-images/peter_molyneux.jpg

Affinity

public://topics-images/p5wlrso8_400x400.jpg

Unity

public://topics-images/unity.png

Deloitte

public://topics-images/logo_of_deloitte.svg_.png

Hitachi

public://topics-images/d5cb3u_d_400x400.png

AltStore

public://topics-images/altstore.jpg

Nobel

public://topics-images/nobel.png

Arduino

public://topics-images/arduino_logo.png

Sora

public://topics-images/img_8233.png

Windows XP

public://topics-images/windows_xp.png

GoPro

public://topics-images/gopro.png

Pikmin

public://topics-images/pikmin.png

Windows 10

public://topics-images/windows_10_logo.svg_.png

Toyota

public://topics-images/toyota-logo.png

iPad Pro

public://topics-images/ipadpro.png

Apple M5

public://topics-images/apple-m5.png

Coral

public://topics-images/coral_symbol.png

Parallels

public://topics-images/parallels.png

Privacy Sandbox

public://topics-images/privacy-sandbox.png

Indiegogo

public://topics-images/352568630_639892788063249_6998682290287321916_n.jpg

GIMP

public://topics-images/wilber-big.png

JavaScript

public://topics-images/unofficial_javascript_logo_2.svg_.png

Xubuntu

public://topics-images/vvrc4lnm_400x400.jpg

Atlas

public://topics-images/atlas_browser.png

Mastercard

public://topics-images/mastercard.png

ICANN

public://topics-images/icann_logo.svg_.png

Halo

public://topics-images/halo-series-logo.svg_.png

Open Source

public://topics-images/open_source_initiative.svg_.png

Grokipedia

public://topics-images/grokipedia.png

Redmi

public://topics-images/redmi.png

SUSE

public://topics-images/suse.png

Superhuman

public://topics-images/img_1132.jpeg

Paramount

public://topics-images/paramount.png

Pat Gelsinger

public://topics-images/img_1172.jpeg

Animal Crossing

public://topics-images/img_1544.png

Magic Leap

public://topics-images/magic_leap_logo.svg_.png

Coca-Cola

public://topics-images/coca_cola.png

PlayStation Portal

public://topics-images/ps-portal.png

Polestar

public://topics-images/polestar.png

Eclipse Foundation

public://topics-images/eclipse-foundation.png

Moonshot AI

public://topics-images/moonshot-ai.png

BioWare

public://topics-images/bioware_2018.svg_.png

Mass Effect

public://topics-images/logo_mass_effect.svg_.png

Red Dead Redemption

public://topics-images/red-dead.png

ROCm

public://topics-images/rocm.png

Reuters

public://topics-images/reuters.png

Battery

public://topics-images/battery.png

Yann LeCun

public://topics-images/357655504_766123181865912_4812354228100980545_n.jpg

Amazon Leo

public://topics-images/leo-logo.png

X

public://topics-images/google-x.png

Steam Machine

public://topics-images/steam-machine.png

Deezer

public://topics-images/deezer_logo.jpg

Windows

public://topics-images/windows.png

Jeff Bezos

public://topics-images/jeff.jpg

The Game Awards

public://topics-images/the-game-award.png

Antigravity

public://topics-images/google-antigravity.png

Nexperia

public://topics-images/vydrpct0_400x400.jpg

Netherlands

public://topics-images/netherland_flag.png

SQLite

public://topics-images/sqlite.png

Rocket League

public://topics-images/rocket.png

AirDrop

public://topics-images/airdrop.png

Cities: Skylines

public://topics-images/cities-2.png

Ai2

public://topics-images/ai2.png

CSA

public://topics-images/csa.jpg

Matter

public://topics-images/matter.png

Apple TV

public://topics-images/appletv.png

Cryptography

public://topics-images/gemini_generated_image_lmurlulmurlulmur-removebg-preview.png

Quick Share

public://topics-images/quickshare.png

PS3

public://topics-images/ps3.png

PDPC

public://topics-images/pdpc.png

Far Cry

public://topics-images/farcry-logo.png

Spring

public://topics-images/spring.png

KDE

public://topics-images/kde.png

SCB 10X

public://topics-images/scb10x.png

Airbus

public://topics-images/logo_blue-copy.png

Nano Banana

public://topics-images/nano-banana.png

teppay

public://topics-images/teppay.png

Absurd Ventures

public://topics-images/absurd.png

IPO

public://topics-images/ipo_font.png

Memory

public://topics-images/media-flash.svg_.png

Synopsys

public://topics-images/bfge93-w_400x400.jpg

MKBHD

public://topics-images/mkbhd.jpg

Let's Encrypt

public://topics-images/lsujvwxu_400x400.jpg

Bun

public://topics-images/bun.png

Z.ai

public://topics-images/zai.png

Kiro

public://topics-images/kiro.png

Binance

public://topics-images/f5y2qenu_400x400.jpg

Total War

public://topics-images/total-war.png

Oxford English Dictionary

public://topics-images/oajpdine_400x400.jpg

Mihoyo

public://topics-images/mihoyo.png

Tekken

public://topics-images/tekken_series_logo.svg_.png

XREAL

public://topics-images/xreal.png

Elastic

public://topics-images/elastic.png

Elasticsearch

public://topics-images/elasticsearch.png

OpenSearch

public://topics-images/opensearch.png

Log4j

public://topics-images/apache_log4j_logo.png

Circana

public://topics-images/circana.png

Terra

public://topics-images/terra.png

Larian Studios

public://topics-images/larian.jpg

Time

public://topics-images/cv44xy5x_400x400.jpg

Control

public://topics-images/control.png

Remedy Entertainment

public://topics-images/remedy.png

Alan Wake

public://topics-images/alanwake-logo.svg_.png

Rockman

public://topics-images/rockman_logo.png

R

public://topics-images/r_logo.svg_.png

System76

public://topics-images/system76.png

Tether

public://topics-images/fzan41qwaae5z82.jpg

iRobot

public://topics-images/ifhlpvr6_400x400.jpg

Team Fortress 2

public://topics-images/tf2.png

Coursera

public://topics-images/cour.png

Truth Social

public://topics-images/400x400ia-75.png

Marissa Mayer

public://topics-images/marissa_new4_400x400.jpg

Ruby

public://topics-images/ruby_logo.svg_.png

Rainbow Six

public://topics-images/_iyt1s_o_400x400.jpg

Coupang

public://topics-images/img_7831.png

Plaud

public://topics-images/img_8489.png

Bose

public://topics-images/bose_logo.svg-3.png

FIFA

public://topics-images/cfum2ynz_400x400.jpg

VSCO

public://topics-images/400x400ia-75_0.png

jQuery

public://topics-images/img_0009.jpeg

TCL

public://topics-images/jblwyp8-400x400.jpg

GitLab

public://topics-images/8kkdkesj_400x400.jpg

John Ternus

public://topics-images/john_ternus.png

Dragon Ball

public://topics-images/db_official.png

AirTag

public://topics-images/airtag1.png

Micron

public://topics-images/img_0696.jpeg

Artificial Intelligence

public://topics-images/robot_for_ai_tag.png

Cainiao

public://topics-images/vqzpygpj_400x400.jpg

Notepad++

public://topics-images/notepad-logo.svg_.png

Crunchyroll

public://topics-images/crunchyroll1.png

NFL

public://topics-images/nfl.jpg

Doraemon

public://topics-images/img_1882.jpeg

Strategy

public://topics-images/2vbrujdh_400x400.png

God of War

public://topics-images/god_of_war-norse-logo.png

Saber Interactive

public://topics-images/saber.png

Castlevania

public://topics-images/castlevania_logo.png

Dead or Alive

public://topics-images/doa_wordmark.png

Android 17

public://topics-images/android-17-icon.png

OpenClaw

public://topics-images/openclaw.png

Vim

public://topics-images/vimlogo.svg_.png

ByteDance

public://topics-images/bytedance_logo_english.svg_.png

Western Digital

public://topics-images/wd_logo.svg_.png

Podcast

public://topics-images/applepodcasts.png

Gentoo

public://topics-images/gentoo.png

Google I/O

public://topics-images/google_io_logo.svg_.png

Fei-Fei Li

public://topics-images/r1ix4qgx_400x400.jpg

World Labs

public://topics-images/lyrgq_kn_400x400.jpg

Manus

public://topics-images/manus.png

Chrome

public://topics-images/google_chrome.png

SanDisk

public://topics-images/sandisk-logo.png

Phil Spencer

public://topics-images/spencer-phil.jpg

TiMi Studios

public://topics-images/timi.jpg

MacBook Pro

public://topics-images/mbp.png

Stripe

public://topics-images/hhdzmj7w_400x400.jpg

Deliveroo

public://topics-images/307858940_5663179810468659_3271454549944860814_n.jpg

Block

public://topics-images/block-logo.png

PS5 Pro

public://topics-images/ps5-pro-icon.png

Leica

public://topics-images/leica_camera_logo.png

iPad Air

public://topics-images/ipadair400.png

Wise

public://topics-images/wiselogo_0.png

Motorola

public://topics-images/moto.png

California

public://topics-images/flag_of_california.svg_.png

Studio Display

public://topics-images/studio_display.png

Macbook Air

public://topics-images/macbookair.png

iPhone 17e

public://topics-images/iphone-17e.png

MacBook Neo

public://topics-images/macbookneo_thumb.png

IETF

public://topics-images/internet_engineering_task_force_logo.svg_.png

Mac Studio

public://topics-images/img_7252.png

United Airlines

public://topics-images/img_7255.jpeg

Meizu

public://topics-images/meizu.svg_.png

Vite

public://topics-images/vitejs-logo.svg-2.png

LINE MAN Wongnai

public://topics-images/line_man_wongnai_logo.jpeg

Wiz

public://topics-images/wiz_logo.svg_.png

Transport Tycoon

public://topics-images/transport_tycoon_coverart.png

Starfield

public://topics-images/starfield_logo.svg_.png

Apple Maps

public://topics-images/apple_maps_ios_26_icon.png

FCC

public://topics-images/fcc.png

Crimson Desert

public://topics-images/crimson-desert.jpg

EverQuest

public://topics-images/eq-logo.png

WHOOP

public://topics-images/whoop.png

Artemis

public://topics-images/artemis.png

Microsoft AI

public://topics-images/microsoft_ai_logo.jpg

EmDash

public://topics-images/emdash.png

Thaicom

public://topics-images/thaicom_logo.png

Security

public://topics-images/40b9ba96-7767-4bdb-ae42-aeec448f5e6a-removebg-preview.png

Meta AI

public://topics-images/meta-ai-logo-2026.png

Greece

public://topics-images/greece-flag.png

iCloud

public://topics-images/icloud1.png

Exteen

public://topics-images/308805805_456316516524882_4999869199557221663_n.png

Intel Atom

public://topics-images/atom_0.png

Core Ultra

public://topics-images/core-ultra.png

Core

public://topics-images/core.png

Baldur's Gate

public://topics-images/baldurs_gate.png

Vercel

public://topics-images/vercel.png

XChat

public://topics-images/xchat_icon.png

BeReal

public://topics-images/bereal.png

FIDO

public://topics-images/mefomyob_400x400.jpg

Passkey

public://topics-images/passkey_icon.png

Lovable

public://topics-images/lovable.png

South Africa

public://topics-images/southafrica.png

Oscar

public://topics-images/the_academy.jpg

Ask.com

public://topics-images/-ef-rbm-400x400.jpg

Singapore Airlines

public://topics-images/img_5314.jpeg

DNS

public://topics-images/dns-removebg-preview.png

Star Fox

public://topics-images/star_fox.png

Civilization

public://topics-images/civ7-logo.png

Eve Online

public://topics-images/eve-online.jpg

Dario Amodei

public://topics-images/dario.jpg

Google Health

public://topics-images/google-health.png

Snapseed

public://topics-images/snapseed.png

Threads

public://topics-images/img_5934.png

LY Corporation

public://topics-images/7a6d4yj-400x400.png

LINE Pay

public://topics-images/594065677_1428215565981607_810088521452480177_n.jpg

on

on

ขอบคุณสำหรับบทความดีๆ ครับ 👍

Azymik Mon, 11/07/2022 - 23:13

ขอบคุณสำหรับบทความดีๆ ครับ 👍

เทคโนโยลี

hisoft Tue, 12/07/2022 - 00:39

โยลี -> โลยี

py' -> ยัง

ขอบคุณสำหรับบทความดีๆครับ

btoy Tue, 12/07/2022 - 08:42

ขอบคุณสำหรับบทความดีๆครับ อ่านแล้วได้ความรู้เพียบเลย

พอเห็นเทคโนโลยีการพัฒนาซีพียูหรือชิปเซ็ตกระโดดก้าวไปไกลแบบนี้ ผมนึกภาพไม่ออกเลยว่า สมมุติมีเด็กนักศึกษาวิศวะคอมไทยคนนึงอยากจะเติบโตไปในอุตสหกรรมนี้ (กับบริษัทยักษ์ใหญ่ระดับโลก) จะต้องพัฒนาตัวเองยังไงถึงจะก้าวไปอยู่จุดนั้นได้

แต่ผมก็จบมานานแล้วเนอะ ข้อมูลในหัวอาจจะล้าหลังไปละ บ้านเราทุกวันนี้มี ม. ไหนที่มี lab ด้าน semicondutor ที่โดดเด่นบ้างครับ

บทความละเอียดมากครับ

PsFreedom Tue, 12/07/2022 - 09:25

บทความละเอียดมากครับ

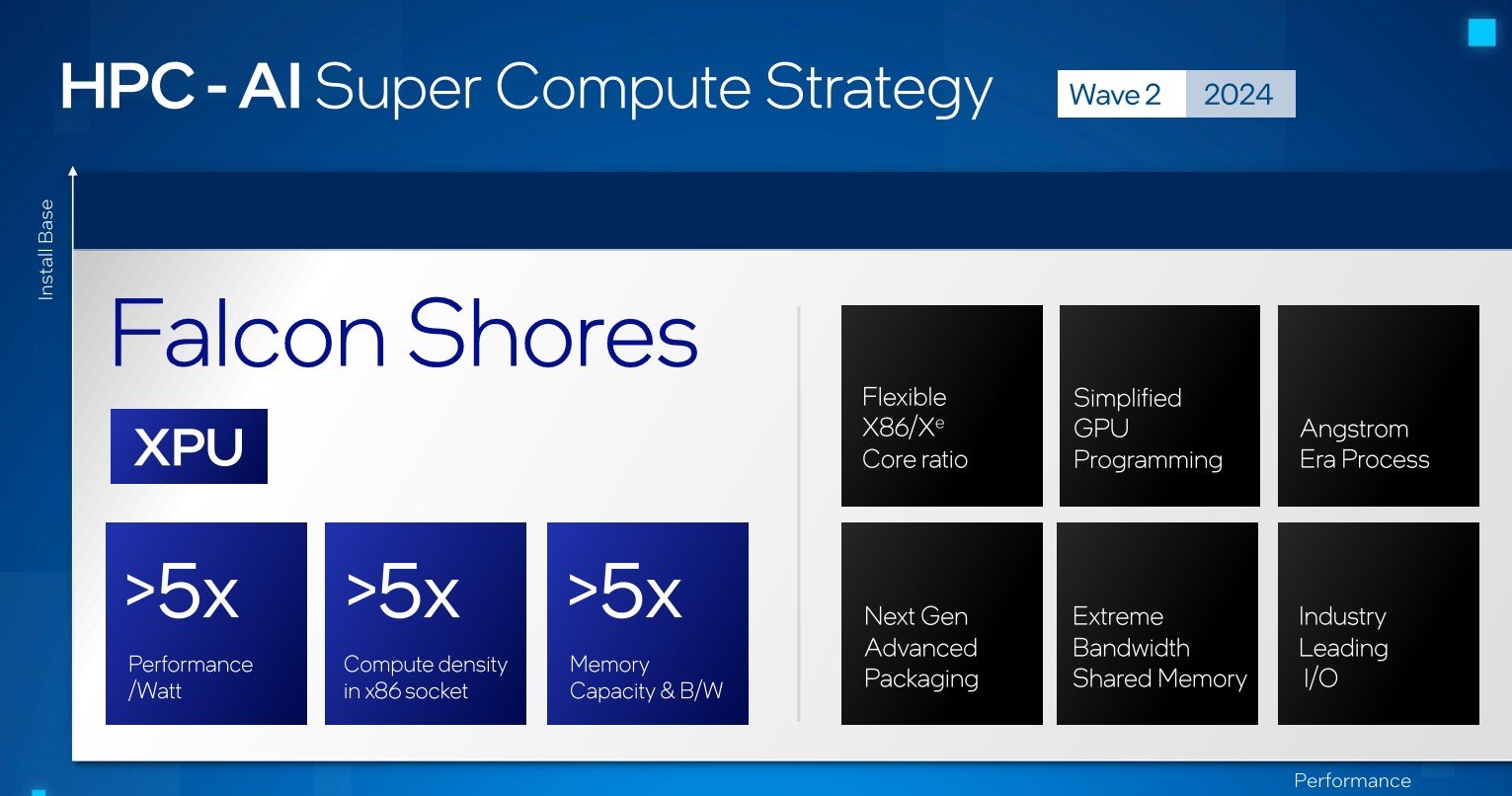

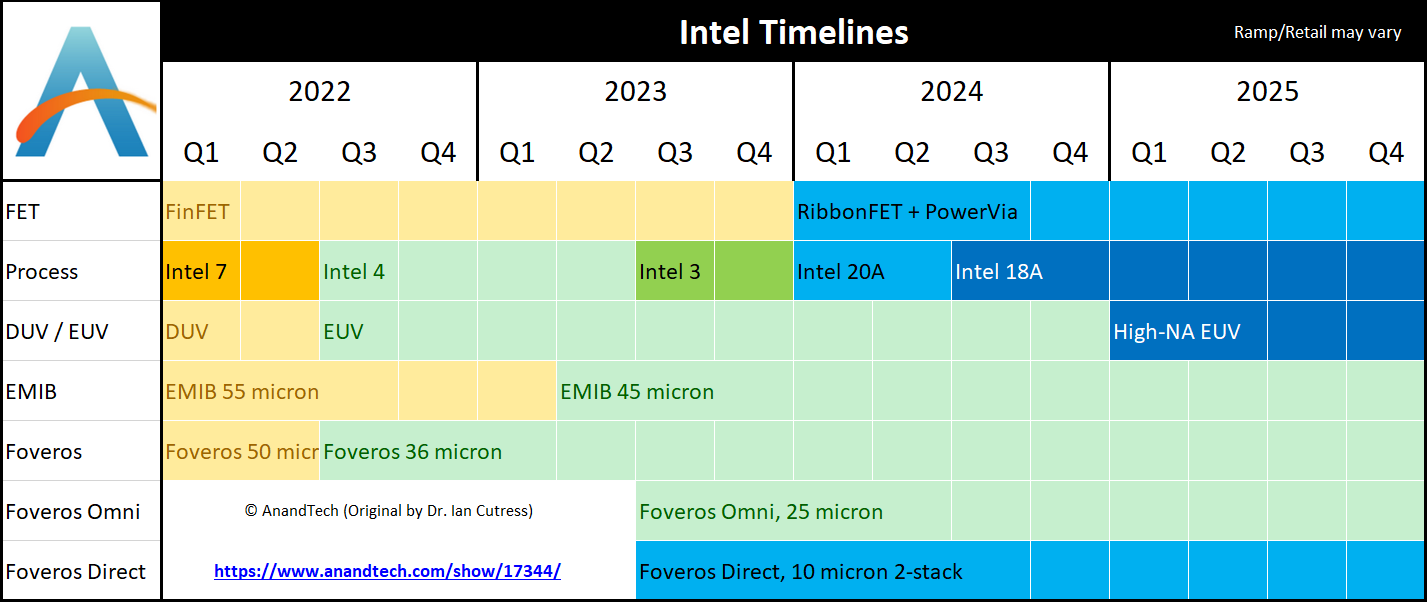

Falcon Shores นี่น่าสนใจ

ผมว่าแนวคิดคล้ายๆ AMD Fusion คือรวม CPU+GPU และใช้ Memory เดียวกัน ไม่ต้องย้ายข้อมูลไปมา ระหว่าง RAM, VRAM ซึ่งถือเป็นคอขวดที่สำคัญของการประมวลผลใน GPU เพราะ (1)ขนาดเล็กไม่พอ (2)ถ้าต้องโอนข้อมูลบ่อยๆ ก็ไม่คุ้ม (3)ทำให้การเขียนโปรแกรมซับซ้อน แต่ AMD Fusion มาก่อนกาลเกินไปหน่อย เทคโนโลยี Chiplets, 3D Stacking ของยุคนั้นก็ยังไม่ดีพอเลยออกมาได้เท่าที่เห็น (ไม่แรง เป็นเป็ด)

ซึ่งมันก็คือสิ่งที่ Apple M1 ทำ

คือวางทุกอย่างเป็น System on Package เลย มี Unified Memory ใช้รวมกัน แถม Apple ไม่สนใจเรื่องการอัพเกรดอยู่แล้ว ก็รวม Memory เข้าไปด้วยเลย (มันก็ยิ่งแรง) แต่ Intel/AMD คงทำสุดโต่งแบบนั้นไม่ได้

ปัญหารอบนี้ไม่ใช่มาเร็วไป

แต่เป็น "มาช้าไป" "จะทันมั๊ย?" "ใครจะใช้?" "จะเกิดมั๊ย?" Intel เป็นบริษัทใหญ่ ตัดสินใจอะไรมันก็ช้า ไม่ทันชาวบ้าน เพราะ GPU computing ตอนนี้ Nvidia CUDA ยึดไว้หมดแล้ว และมี AMD Instinct (OpenCL) เล็กน้อย ส่วน Xe Core และ oneAPI จะไปลงตรงไหน?

บางทีของมันดีแต่ไม่มีคนใช้ (Google Plus, Windows Phones, etc.) นักพัฒนาไม่อยากย้าย ไม่อยากทำใหม่ ก็เหมือนที่คนยังติดอยู่กับการใช้ Windows/x86 นั่นแหละ (Intel ก็คงเข้าใจดี ใช่ไหมล่ะ 555) Intel คงต้องใช้กำลังภายในมากหน่อยรอบนี้ เอาจริงๆ ในบทความเก่าก็พูดไว้แล้ว

มองในแง่หนึ่ง AMD ก็ทำ UMA

mr_tawan Wed, 13/07/2022 - 14:08

In reply to บทความละเอียดมากครับ by PsFreedom

มองในแง่หนึ่ง AMD ก็ทำ UMA ไปแล้วใน console แต่คิดว่าที่ไม่ทำบน PC น่าจะเกิดจากฝั่ง OS ตรงนี้คงต้องไปทำงานร่วมกับ OS vendor ให้รองรับด้วย

คิดว่าที่ Fusion ไม่ไปถึงขั้น UMA (ทั้ง ๆ ที่อยู่ในแผนแต่แรก) ก็เพราะ OS นี่ล่ะครับ

แข่งกันพัฒนา ดีครับ

best Tue, 12/07/2022 - 12:23

แข่งกันพัฒนา ดีครับ

อ่านเพลินมากครับ

modernelf Tue, 12/07/2022 - 18:49

อ่านเพลินมากครับ ถึงแม้จะไม่ค่อยเข้าใจโลกเทคโนโลยีฝั่งเท่าไรก็ตาม

เมื่อได้วิศวกรลูกหม้อกลับมาเป

akira Thu, 14/07/2022 - 08:57

เมื่อได้วิศวกรลูกหม้อกลับมาเป็น CEO แถมยังได้วิชาการตลาดจากการไปเป็น CEO บริษัทภายนอก มันก็จะอย่างนี้แหล่ะ ต้องยกนิ้วให้บอร์ดชุดปัจจุบันที่มองขาดหาคนที่คนอื่นมองไม่เห็นกลับมาช่วยบริษัทที่กำลังเหนื่อย คล้าย Microsoft ที่พลิกสถานการณ์ได้ บริษัทที่มีแนวโน้มเป็นบริษัทร้อยปี มันต้องมีบอร์ดที่ตาคมหาคนเก่งมาทดแทนได้ถูกที่ถูกเวลา

บริษัท startup ก็เช่นกัน ไม่ใช่ founder เก่งแล้วจบ มันต้องมีผู้สนับสนุนที่มีสายตาคมมองคนขาด เพื่อหาคนมาทดแทน หรือเสริมกรณีที่ founder เหนื่อยล้า

ผู้นำ ≥ CEO ≥ Manager ที่เก่งยังสำคัญต่อองค์กร ถ้ามีคนเดียวกันหาคนมาช่วยซะ แล้วคุณจะรอด

ทำมาครับ รอซื้อ

gamoman Fri, 15/07/2022 - 18:34

ทำมาครับ รอซื้อ ขอเย็นและประหยัดไฟ